En los últimos años, los sistemas de videovigilancia digital se han utilizado ampliamente en diversos campos, como bancos, carreteras y edificios. En los sistemas de videovigilancia digital, la tecnología OSD (On Screen Display) es una parte indispensable. OSD proporciona a los usuarios una interfaz hombre-máquina amigable, lo que permite a los usuarios obtener más información adicional.

1 Composición del sistema

El sistema presentado en este artículo es un sistema de videovigilancia completo basado en TI DSP TMS320DM6? 3 y FPGA. Admite 1 canal de entrada de video y 1 canal de salida de video, y también proporciona una interfaz de red.

La entrada de video se realiza mediante el rentable decodificador de video TVP5150A de TI. TVP5150A puede realizar la colección de dos entradas de video compuesto o una señal de video S-video. El registro se configura a través de I2C y la señal de video digital de salida sigue el estándar ITU656.

La señal de video digital decodificada por TVP5150A se transmite al DSP a través del puerto de video 1 de DM6? 3, y el DSP realiza el procesamiento de vídeo necesario y, a continuación, la interfaz de red lo envía al dispositivo remoto. Por otro lado, ¿después de DM6? 3 procesa los datos de video recibidos de la red, SAA7105 los muestra y envía a través del puerto de video 2 a través de FPGA.

La parte de salida es realizada por SAA7105. SAA7105 es un codificador de video de alto rendimiento de NXP Company, que puede proporcionar salida de video compuesto, salida de video VGA y salida de señal de video de alta definición HDTV. El control de SAA7105 también se realiza a través de I2C, y recibe la señal de video digital del estándar compuesto ITU656.

La parte de procesamiento de video adopta DSP TMS320DM6 3 de TI para realizar. La frecuencia principal de DM6? 3 puede alcanzar 600MHz, y hay dos puertos de video de 20 bits. Los puertos de video admiten interfaces de video digital como BT.656 e Y / C. DM6-3 también integra la red MAC para realizar el acceso a la red.

La velocidad de desarrollo del rendimiento del hardware siempre es difícil de satisfacer las necesidades del software. En las aplicaciones cada vez más complejas del procesamiento de video, DSP es responsable de tareas complejas de procesamiento de video y los recursos se vuelven muy limitados. Por lo tanto, en el diseño de este sistema, FPGA se utiliza para realizar el diseño de OSD, que puede reducir la carga de DSP.

La parte de implementación de OSD utiliza XC3S250E de Xilinx. XC3S250E es un FPGA de la serie Xilinx SPARTAN-3E con 250,000 puertas lógicas.

2. Implementación de OSD

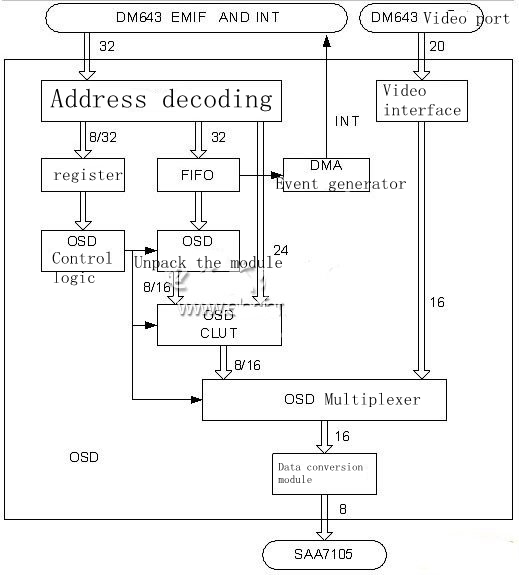

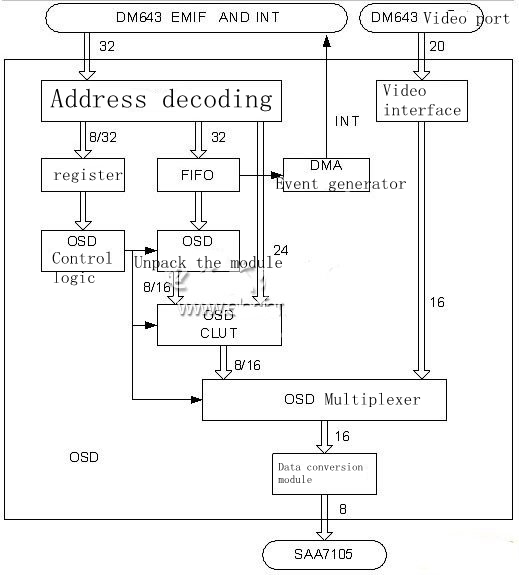

SAA7105 no puede realizar la función OSD, pero la realiza XC3S250E. ¿El chip de control principal DM6? 3 solo necesita informar a la FPGA del contenido y la posición que se mostrará, y el trabajo específico lo realiza la FPGA. El diagrama de bloques lógico de OSD se muestra como en la Fig.2.

OSD FPGA recibe datos OSD e instrucciones de control desde DSP DM6 3 a través de EMIFA, recibe datos de video a través del puerto de video DSP 1, superpone información OSD en los datos de video y los envía al codificador de video SAA7105. Los módulos funcionales de OSD se describen a continuación.

El puerto de datos del módulo de decodificación de direcciones está interconectado con los datos bajos de 32 bits de EMIFA de DSP DM6 3, y recibe los datos y la información de control enviada por DM6 3. Estos datos y la información de control son los datos originales de 32 bits enviados por DM6 3. El módulo de decodificación de direcciones coloca los datos OSD recibidos, como el contenido del OSD, en el FIFO interno de la FPGA en un formato de datos de 32 bits. La información de control se utiliza principalmente para controlar el OSD a través de un conjunto de registros de control.

También hay un módulo de interfaz de video directamente conectado al DSP. El módulo de interfaz de video está conectado al puerto de video 2 del DSP y almacena los datos y la información de control del puerto de video DSP. Esta información de control se transmite directamente al módulo de control multicanal OSD, y la información de control también controla directamente el decodificador de video SAA7105.

La lógica de control del OSD envía la información de control obtenida del grupo de registros de control a cada módulo funcional del OSD para realizar el control del OSD. El grupo de registros se divide principalmente en dos partes: una es el grupo de registros asíncronos, que envía información de control como restablecer, habilitar OSD y seleccionar el ancho de datos al OSD; el otro es el grupo de registros síncronos, que controla principalmente la información de posición del OSD.

El módulo de decodificación OSD extrae los datos que se mostrarán del FIFO de acuerdo con la información de control de la lógica de control y los envía al módulo OSD CLUT en sincronización con los datos de video. Los datos obtenidos de FIFO son los datos originales de DSP de 32 bits, y los datos requeridos por el módulo OSD CLUT son de 8/16 bits, por lo que el módulo de desempaquetado de OSD necesita descomprimir los datos de 32 bits de acuerdo con la frecuencia de la puerto de video. Los datos de 32 bits se transmiten al módulo OSD CLUT con un ancho de 8/16.

Otra función del módulo FIFO es transferir información de estado FIFO al módulo generador de eventos DMA, como FIFO lleno o FIFO vacío. El generador de eventos DMA monitorea estos eventos y, si ocurren, se envían a DM6? 3 en modo de interrupción para lograr operaciones de lectura y escritura correctas en el FIFO.

El módulo OSD CLUT busca el valor correspondiente de YCbCr para los datos de cada píxel recibido del módulo de desempaquetado OSD y controla la secuencia de salida de estos datos OSD CLUT. Esta relación de conversión es transmitida por el DSP a través del puerto de datos de 24 bits. Los datos del módulo OSD CLUT se envían directamente al módulo controlador multicanal OSD.

El módulo de control multicanal OSD determina los datos de vídeo de salida de acuerdo con el bit de control Alpha recibido del módulo OSD CLUT. Si la información de OSD actual, es decir, el bit de control Alpha es válida, envía los datos de OSD al módulo de conversión de datos. De lo contrario, envíe los datos de video originales recibidos desde el módulo de interfaz de video para realizar la función OSD.

La salida de datos por el controlador multicanal OSD no se envía directamente al decodificador de video, pero a través del módulo de conversión de datos, de acuerdo con las condiciones específicas de la aplicación, se realiza la conversión de formato de datos necesaria. Se puede ver en la sincronización de la interfaz de SAA7105 que cuando SAA7105 está configurado para salida de video compuesto, los datos requeridos son datos de borde de reloj único. En este momento, el módulo de conversión de datos no funciona y los datos recibidos del módulo de control multicanal OSD se transmiten intactos. Para SAA7105; si SAA7105 está configurado en modo de salida VGA o HDTV, se requieren datos de borde de reloj dual. En este momento, el módulo de conversión de datos convierte los datos de borde de reloj único recibidos desde el controlador OSD en datos de borde de reloj dual y los envía al decodificador de video SAA7105.

Se puede ver que FPGA ha completado todo el trabajo de OSD. Si desea mostrar el contenido OSD, DM6? 3 solo necesita enviar instrucciones de control a la FPGA a través del puerto EMFIA. Estas instrucciones, por supuesto, incluyen el contenido y la información de ubicación del OSD.

3. Control de OSD

El diseño OSD implementado por XC3S250E realiza la visualización del OSD en función de la ubicación del OSD recibida y la información del contenido, sin ninguna restricción en el contenido mostrado por el OSD, que es muy flexible y conveniente. A continuación, se toma la visualización de caracteres chinos OSD como ejemplo para ilustrar la operación de control de OSD.

Para mostrar los caracteres chinos correctamente, el código interno del carácter chino ingresado debe convertirse en el código de ubicación correspondiente. Para esta función, usamos la función Uint32 Code_Converse (unsigned char * CodeNPointer), cuya entrada es un puntero, apuntando al carácter chino a convertir. El valor de retorno es el código de ubicación correspondiente al carácter chino. La visualización OSD se realiza mediante la función OSDHZ? Isplay:

anular OSDHZ_ Display {

Uint8 * pFrame

Paso Uint32

OSDUTIL_Point * loc

Uint32 Código Q

Fuente OSDHZ? Ont *

Uint8 fgColor

Uint8 bgColor

}

Entre ellos, Uint8 * pFrame es el búfer de búfer para la salida OSD; El tono Uint32 es el valor de píxel que se muestra en cada línea; OSDUTIL_Point * loc es la posición de visualización del primer carácter; Uint32 CodeQ es el código de área para mostrar caracteres chinos; La fuente OSDHZ? Ont * es la fuente utilizada para mostrar caracteres chinos; Uint8 fgColor muestra el color de primer plano de los caracteres chinos; Uint8 bgColor muestra el color de fondo de los caracteres chinos.

Por lo tanto, si necesita mostrar caracteres chinos, solo necesita convertir los caracteres chinos al sistema de código necesario y luego enviar el código de área convertido al OSD FPGA. Por supuesto, para mostrar caracteres chinos, la biblioteca de caracteres chinos es indispensable.

Nuestro otro producto: